Combining a CPU core, DSP core, and numerous video accelerators, new additions to the Texas Instruments (TI) DaVinci video-centric processor line target applications ranging from personal media players to multi-channel digital video recorders and professional broadcasting systems. The new chips comprise two families: The TMS320CDM814x (DM814x) family is optimized for low power consumption; these chips support a single video channel at 1080p resolution and 60 frames per second (fps), or three channels at 720p 30 fps. The TMS320CDM816x (DM816x) family is optimized for performance and supports up to three 1080p 60 fps video.

The new DaVinci products are based on an ARM Cortex-A8 CPU core that operates at 1.2 GHz (DM816x) or 1 GHz (DM814x). A TMS320C674x fixed- and floating-point DSP core operating at 1 GHz (DM816x) or 750 MHz (DM814x) adds support for audio codecs and other math-centric signal-processing algorithms, including video analytics algorithms.

Some members of both of the new processor families integrate an Imagination Technologies SGX530 graphics accelerator that supports 1920×1280-pixel resolution and can drive dual displays. Integrated peripherals include SATA 2.0, gigabit Ethernet, PCI Express (PCIe) and HDMI interfaces.

The chips include substantial on-chip memory along with an interface to external DDR3 DRAM. Each of the video accelerators includes a 256 kbyte memory array. The ARM and DSP cores include caches. And there is a shared 512 kbyte SRAM block that all processing resources can access.

TI had previously announced a DM8168-badged chip one year ago, offering the product specifically for digital surveillance applications. The newly expanded product family is now being offered for a broader array of video-centric applications and is sampling to customers. The DM816x family is available in four flavors—with varying numbers of video accelerators and with or without the graphics accelerator, starting at around $75 (quantity 1,000).

The DM814x family will sample in the third quarter of this year. It will be available with or without the graphics accelerator for around $50.

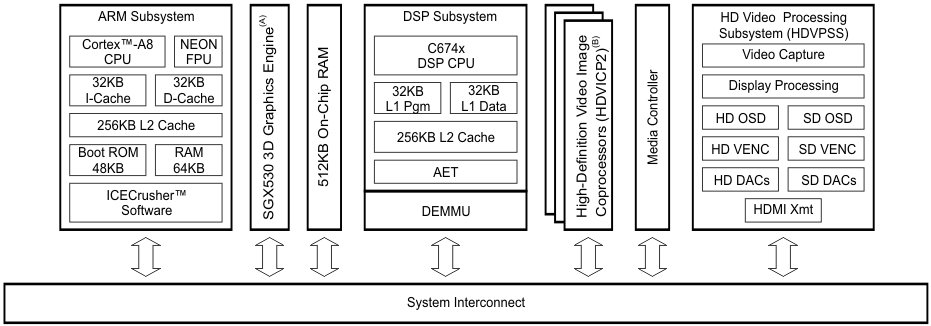

A block diagram of the processor and accelerator complex in the DM816x is pictured in Figure 1 below. In addition to the ARM and DSP cores, note the three video coprocessors along with the HD Video Processing Subsystem (HD-VPSS). The coprocessors and HD-VPSS are key to enabling high-resolution video processing.

Figure 1. The processor and accelerator complex in the DM816x family includes two or three coprocessors that support popular codecs and a video processor subsystem that implements pre- and post-processing functions.

The coprocessors and HD-VPSS enable video encoding, decoding, capture, and display of real-time video streams. The HD-VPSS handles the capture function and feeds output streams to the displays, including items such as overlays or on-screen-display elements from the graphics accelerator.

The HD-VPSS also performs pre- and post-processing functions on the video streams. For example, the unit can handle format conversions, de-interlacing, scaling, and color-space conversion. The HD-VPSS unit can also enhance image quality via noise filtering, de-ringing, and edge and detail enhancement.

The video coprocessors provide support for selected popular video codecs, including MPEG-1/2/4, H.264, Microsoft’s VC-1, RealVideo’s RV9/10, the open-source AVS-1.0 codec, and Google’s VP8 (acquired from On2 Technologies). Other codecs are supported via software implementations that don’t use the coprocessors, and therefore will achieve lower performance.

The new additions to the DaVinci family target a broad range of applications. For the DM816x, target applications include multi-channel DVR security systems, video-conferencing systems, and professional broadcasting systems with multiple displays. The DM814x targets digital-signage, portable-medical-imaging, and personal-media applications, among others. Many of these target applications require video analytics algorithms, such as object detection and tracking. The DSP core is intended to be used for such functions. According to TI, the new chips can handle motion detection, object detection, face recognition, tamper detection, and video tracking algorithms. (The HD-VPSS block helps enable effective analytics by cleaning up the video stream through operations such as noise reduction and edge sharpening.)

TI manufactures the DM814x in a low-leakage 45 nm process resulting in chips that will consume around 3 W, according to TI. The company is making the DM816x family using a high-performance 40 nm process. According to TI, the chips will range in power consumption from 12 to 15 W.

TI is also touting the new chips as pin-to-pin and software compatible with the Integra and Sitara processors announced last year. In concept, this lineage gives design teams a way to design one system that can address a broad range of performance and price points by swapping processors. The Sitara family includes only an ARM core, while the Integra adds a DSP core, and the new DaVinci chips add video coprocessors and the HD-VPSS.

Design teams will shortly have the tools needed to start development efforts. TI has begun taking orders for the $1995 TMDXEVM8168 evaluation module and pledges to ship the product in April. The kit ships with Linux and supports the OpenMax API. TI has pledged Google Android support in the second quarter of this year, followed by Microsoft Windows Embedded support in the third quarter.

If the new DaVinci chips live up to their specifications, they will offer impressive performance and integration for many video applications. However, most of the performance in these chips comes from non-user-programmable coprocessors and accelerators. Hence, applications that can’t make use of the functions supported by the coprocessors and accelerators will have significantly lower performance. In addition, the complex architectures of these SoCs—with a CPU, DSP, and multiple coprocessors and accelerators—means that extracting the full performance potential will likely be challenging; the quality of TI’s tools, reference designs, and related development resources will be critical to the success of TI’s customers.

Add new comment