Last month's edition of InsideDSP discussed MIPS' recent three-core Aptiv product family announcement and provided detailed information on the high-end proAptiv offering. This follow-up article will cover the mid-range interAptiv and entry-level microAptiv cores. As with proAptiv, ARM is clearly in MIPS' gunsights with both of these new architectures.

interAptiv

MIPS' interAptiv core, which like proAptiv will be available by early next quarter, is intended to compete with the ARM Cortex-A5 and Cortex-A7. As such, MIPS touts the core's multi-threading support, which the ARM competitors lack, and which transforms each physical core into two virtual cores (with up to four physical cores possible in an interAptiv-based SoC). Optional QoS support ensures that particular threads are processed in a predictable timeframe. interAptiv integrates an L2 cache controller and memory array, ranging in size from 256 KBytes to 8 MBytes, leading to a cache access latency reduction of more than 2x versus the non-integrated L2 cache in MIPS 1004K and 1074K core precursors.

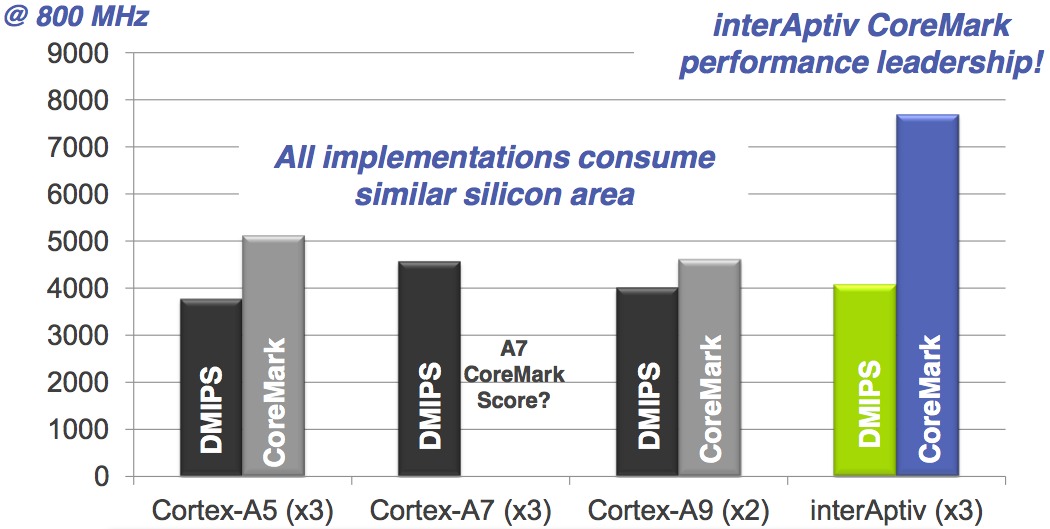

Figure 1. A tri-core interAptiv configuration, MIPS believes, stacks up favorably from a performance standpoint against a dual-core ARM Cortex-A9 alternative approach at comparable clock speeds, while consuming comparable silicon area. Note, however, that MIPS is not necessarily claiming that interAptiv will be able to achieve comparable maximum clock speeds to the ARM core competitor

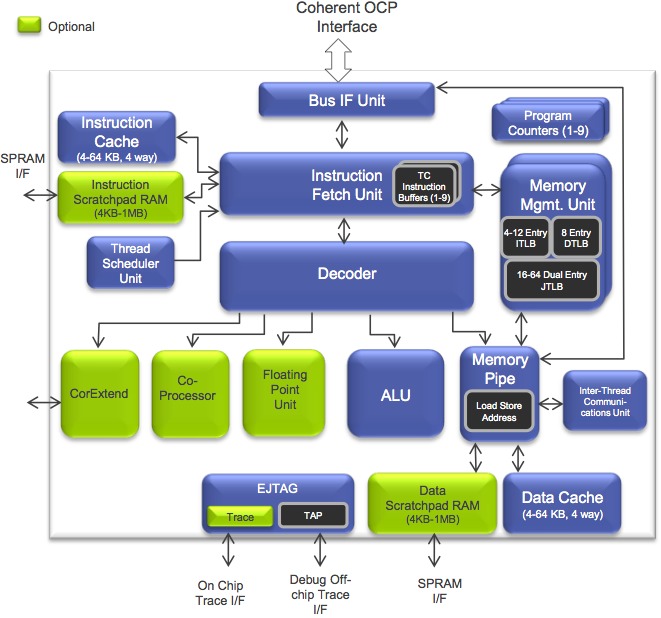

Like proAptiv, interAptiv offers the Cluster Power Controller for per-core voltage and clock management in multi-core configurations. interAptiv implements a nine-stage in-order pipeline, and supports an optional multi-threaded IEEE-754 floating point unit; the DSP ASE SIMD processing engine again comes standard (Figure 2). On TSMC's 40G process, without employing low VT transistors, OD (oxide diffusion) or other specialized techniques, MIPS forecasts interAptiv to run at greater than 1 GHz clock speeds. Dispensing with the DSP ACE function block, and employing design and process optimizations, can boost operating frequencies up to 1.5 GHz, MIPS believes.

Figure 2. interAptiv is capable of multi-threading, including optional thread QoS control, neither of which is supported by ARM's Cortex-A5 or Cortex-A7

microAptiv

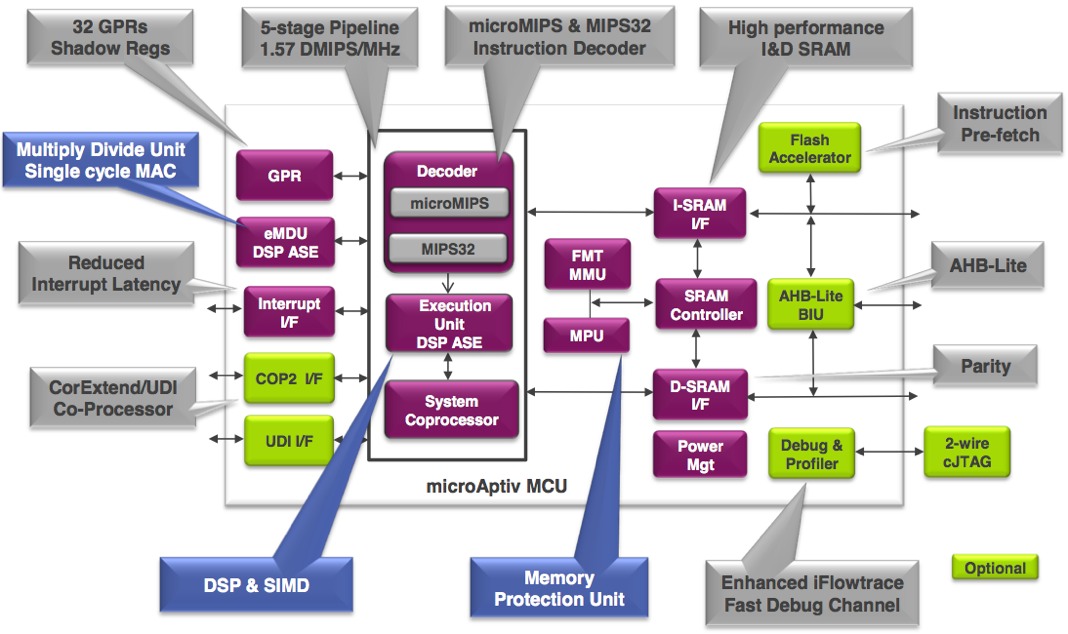

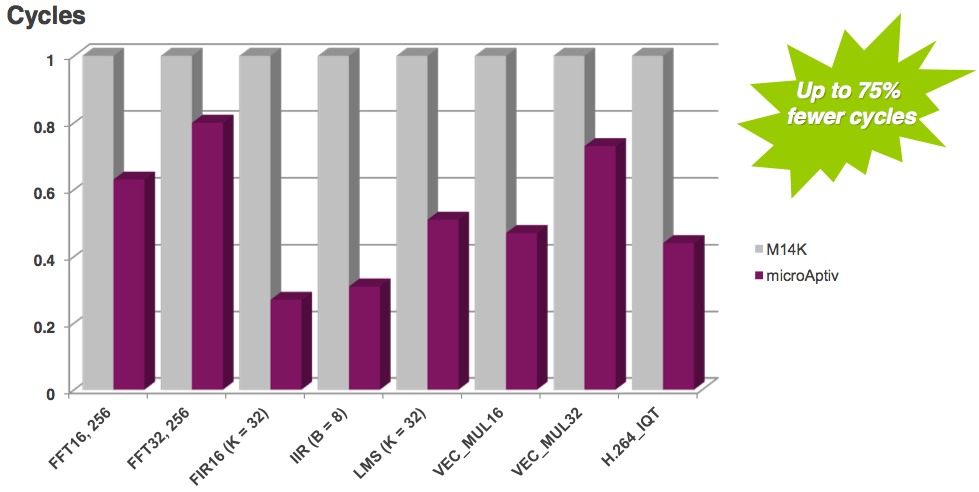

MIPS' microAptiv core is based on the prior-generation M14K/c cores, with the addition of microMIPS code compression support and the DSP ASE function block. It comes in both cache-less (microcontroller) and cache-inclusive (microprocessor) variants (Figure 3).

Figure 3. The microAptiv core comes in both cache-less microcontroller (upper) and cache-inclusive (lower) microprocessor versions

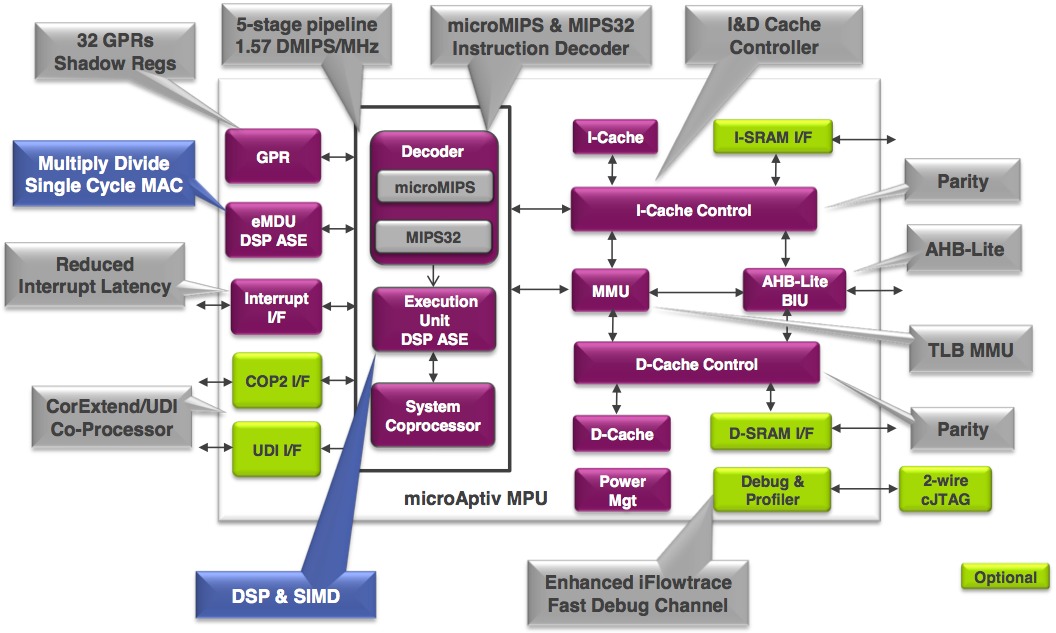

microAptiv implements a 5-stage in-order pipeline, with 10-cycle interrupt latency. And, of particular interest to digital signal processing applications, microAptiv incorporates the DSP ASE instruction set extensions, bringing DSP capabilities to a full generational range of MIPS cores for the first time (Figure 4).

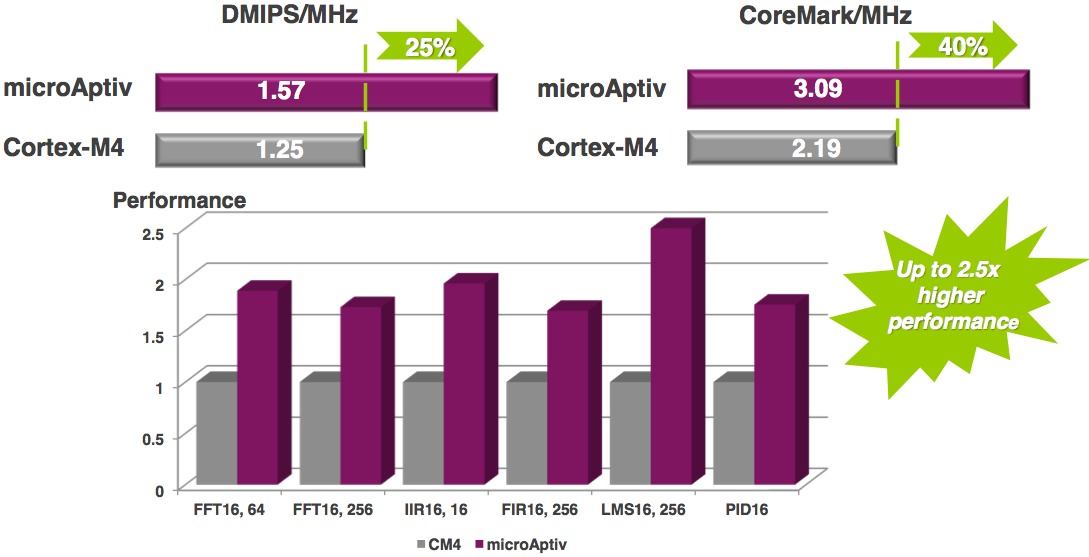

Figure 4. MIPS claims that the DSP ASE instruction set extensions, support for which for the first time extends across the company's entire latest-generation core line, enables microAptiv to outperform earlier MIPS cores (upper) and ARM's Cortex-M4 (lower) at comparable clock speeds, and on both general-purpose benchmarks and various digital signal processing functions

DSP ASE comprises four accumulator register pairs, supporting fractional data types and saturating arithmetic. Its 70 SIMD instructions simultaneously operate on two 16-bit or four 8-bit packed operand sets. DSP ASE provides 159 DSP-tailored instructions, 38 of which are of the multiply or MAC (multiply-accumulate) variety, and delivers single-cycle throughput.

MIPS points out that ARM's Cortex-M4, which the company views as the primary microAptiv competitor, uses a three-stage pipeline architecture with no cache- or MMU-inclusive variant offered. Cortex-M4, according to MIPS, also offers no dedicated DSP multiply/divide or accumulator units, half the number of total instructions, DSP-tailored instructions and SIMD instructions, along with fewer multiply/MAC instructions. microAptiv is now available for use in SoC designs; performance, size and power consumption approximations for various core configurations on several TSMC process nodes are shown in Table 1.

|

|

MCU |

MCU |

MPU |

|

Process |

90LP |

65LP |

65G |

|

Operating Frequency (MHz) |

235 |

380 |

500 |

|

Core area (mm2) |

0.42 |

0.24 |

0.33 |

|

Core active power (mW/MHz) |

0.16 |

0.08 |

0.1 |

Table 1. Target specifications of various microAptiv core implementations

As with proAptiv, the interAptiv and microAptiv cores are logical next-generation evolution steps for current MIPS licensees. But the motivation for existing ARM licensees to consider an evolution to the alternative MIPS ecosystem is less clear, notwithstanding MIPS’ need to win over ARM licensees in order to reverse its recent market share slide. Perhaps MIPS' greatest chance of success, therefore, is with microAptiv, which competes not only against low-end ARM offerings but also against microcontroller cores from other suppliers, and does so with tangible differentiation by virtue of its fuller-featured DSP ASE capabilities.

Add new comment