Back in early 2013, the smartphone market was red hot, as was demand for Amazon's Kindle and other e-book readers. And the tablet market, although comparatively nascent, was in a rapid growth phase, as was interest in alternative computer platforms such as Google's Chrome O/S-based products. The substantial processing demands of these and other similar applications are evident in the formidable resources integrated within Freescale Semiconductor's i.MX 6 family introduced that same year: one to four ARM Cortex-A9 cores running at 1+ GHz speeds, plus 2D, 3D and/or vector graphics processing cores and optional image and video processing units.

Fast-forward to today, and the picture looks different. Smartphone sales are beginning to plateau; tablet sales have already done so. And the capabilities of a dedicated e-book reader are increasingly being subsumed into the feature set of the multi-function tablet. Nowadays, wearable devices—smart watches, fitness bands, and maybe (someday) even smart glasses—and IoT devices are the hot product categories. The feature set of the recently introduced first two members of Freescale's i.MX 7 SoC family has correspondingly been scaled back and tailored to match these applications' needs as well as those of the broader embedded market (Figure 1).

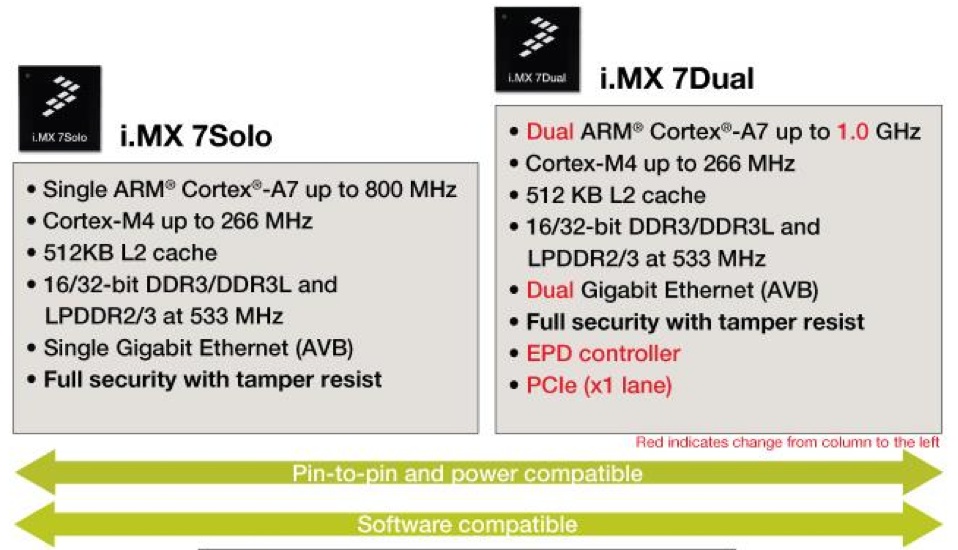

Figure 1. The comparatively modest CPU cores and other on-chip resources of Freescale's first two i.MX 7 family members reflect their redirected market focus versus i.MX 6 precessors.

The generational repositioning begins with the CPU subsystem. This time you'll find a single 800 MHz (i.MX 7Solo) or dual 1 GHz (i.MX 7Dual) ARM Cortex-A7 primary CPU. The Cortex-A7 is a feature set and performance back-step versus the Cortex-A9 precursor, as InsideDSP's November 2011 coverage points out, although Freescale's Business Development Manager Nik Jedrzejewski noted during a recent product briefing that the two-Cortex-A7 arrangement of the i.MX 7Dual (each 1.9 DMIPS/MHz peak) potentially delivers significantly higher performance than a single Cortex-A9 alternative (2.5 DMIPS/MHz peak), at notably lower comparative power consumption. And whereas the Cortex-A7 is the "little" member of ARM's 32-bit big.LITTLE paired-core scheme, in i.MX 7 it's the bigger of the two processor cores.

Handling less- performance-demanding scenarios in this case is a 266 MHz ARM Cortex-M4. From a digital signal processing standpoint, the Cortex-M4 doesn't included the enhanced capabilities of the follow-on Cortex-M7. However, the Cortex-M4 does support a subset of the NEON SIMD instruction set, and because Freescale's SoCs embed the Cortex-M4F variant, a single-precision floating point unit is present. Note, too, that the Cortex-A7, with a complete NEON SIMD implementation along with its own FPU, is always available for use instead.

When asked why his company went with the Cortex-M4 instead of the newer Cortex-M7, Jedrzejewski first pointed out that i.MX 7 is a development follow-on to the i.MX 6SoloX, Freescale's first heterogeneous-architected application processor, which was also Cortex-M4-based. When the i.MX 6SoloX was being defined, the Cortex-M7 was not yet available. Development momentum aside, Freescale did evaluate the upgraded Cortex-M7 this time, along with the lower-end Cortex-M0+, but determined that the Cortex-M4 still delivered the optimum combination of performance, size and power consumption for these particular SoCs.

Regarding ARM's big.LITTLE alternative heterogeneous processing approach, Jedrzejewski noted that ARM's intent is to run a full-featured operating system on either core. In Freescale's case, the Cortex-M4 won't be challenged with such robust demands. In fact, an integrated resource domain controller enables assignment of various on-chip peripherals to either processor core (peripherals can also be shared between the cores), creating the implementation possibility for the Cortex-M4 to run a "sandboxed" software environment immune from vulnerabilities which might plague code running on the Cortex-A7 primary CPU.

Onboard both i.MX 7 family members you'll find 512 KBytes of L2 cache for the Cortex-A7 (shared between the two cores in the i.MX 7Dual) and 64 KBytes of zero-wait-state SRAM for the Cortex-M4, along with 256 KBytes of general-purpose SRAM and 96 KBytes of ROM. Also included are a hardware security processor integrating random number generation, cryptographic cipher and tamper prevention capabilities, a Gigabit Ethernet MAC compatible with the Audio Video Bridging (AVB) specification and tailored for IoT "edge" products, memory controllers for DDR SDRAM and NOR, NAND and SPI serial flash memory, and other peripherals. The i.MX 7Dual adds a second GbE MAC, enabling its use as an IoT "gateway" processor, along with a x1 PCI Express controller and an Electronic Paper Display (EPD) controller. The pixel processing pipeline unit found in the i.MX 6SoloLite and i.MX 6SoloX has been retained in both i.MX 7 devices, although the fuller-featured image processor unit (IPU), video processing unit (VPU) and 2D, 3D and vector graphics processor cores (GPUs) found in higher-end i.MX 6 processors are gone. Jedrzejewski notes that the IPU, VPU and GPUs will likely make a return in follow-on i.MX 7 products now in development.

Although i.MX 7 doesn't deliver "raw" performance comparable to i.MX 6 predecessors of similar primary processor core counts, Jedrzejewski points out that the new chips’ target markets have more modest performance needs. Conversely, the new chips' target applications' power consumption requirements are even more stringent than before, and i.MX 7 delivers a solid response based on the company's published specifications. In active mode, i.MX 7 devices' primary processor cores are 3x more power-efficient than those in i.MX 6 precursors, according to Freescale, at 15.7 DMIPS/mW per core. Each Cortex-A7 core draws only 100 μW/MHz, with the Cortex-M4 drawing an even stingier 70 μW/MHz. And the improvements continue in standby: the 28 nm-fabricated chips' 250 μW Low Power State Retention mode, enabled by finer-grained power domain subdivision within the SoCs, is 1/3 the power consumption of its mode counterpart in 40 nm-based i.MX 6 devices.

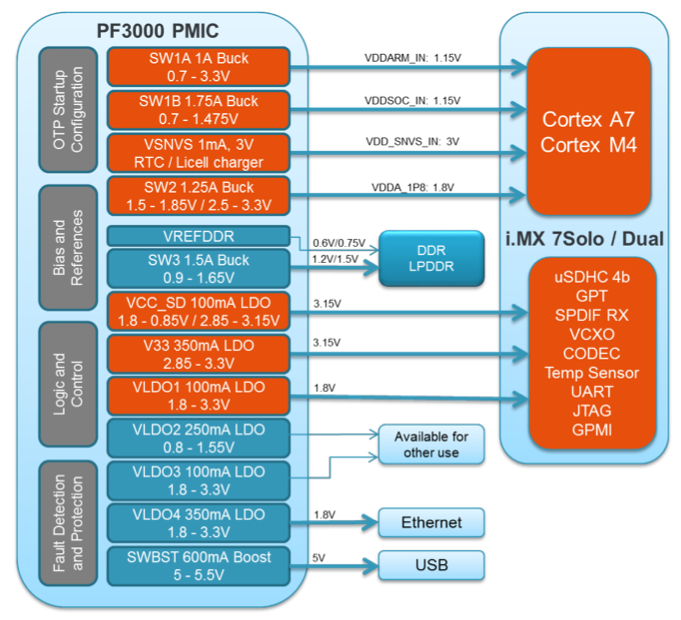

Coordinating the generation and sequencing of the multiple required voltages is the companion PF3000 power management IC (PMIC), available in consumer, industrial and automotive qualification grades and now in production, along with two board designs, the KITPF3000FRDMEVM evaluation board and KITPF3000FRDMPGM programming board (Figure 2). PF3000 pricing ranges from $1.83 to 1.92 in 10,000-unit volumes. The i.MX 7Solo and i.MX 7Dual are now sampling, with full production forecasted for November. According to Freescale, the i.MX 7 family will be priced alongside lower-end i.MX 6 derivatives, with all i.MX 7 variants available below $10 in high volumes.

Figure 2. Freescale's i.MX 7 low power consumption potential is only realizable in conjunction with fine-grained, precise sequencing of supply voltages for various chip subsystems in various operating modes, the responsibility of the company's PF3000 power management IC.

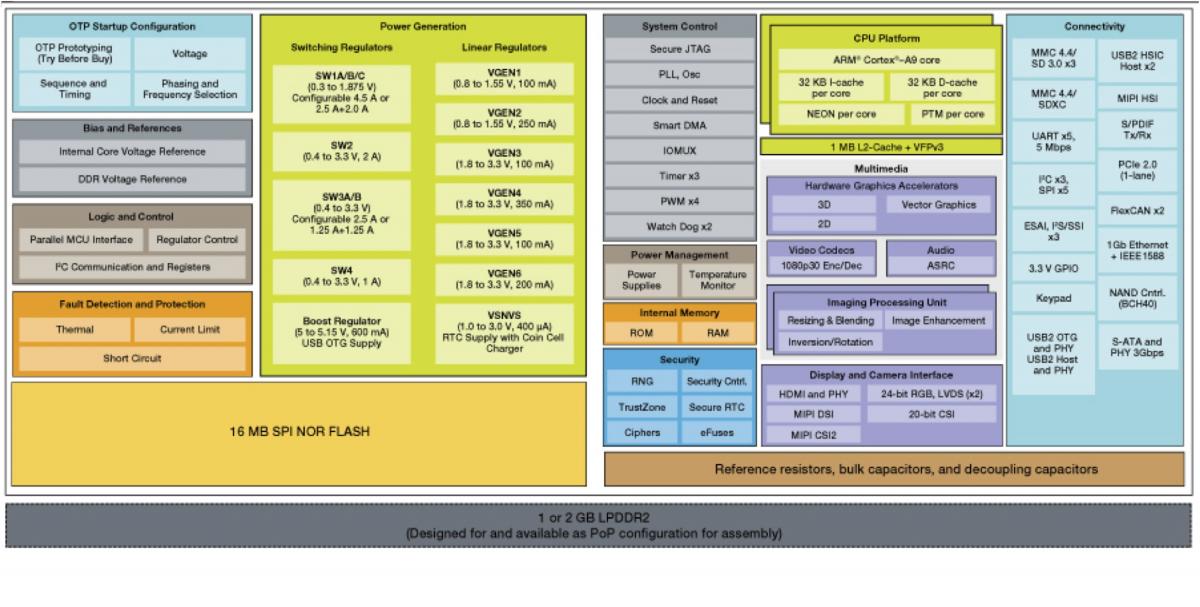

Although i.MX 7 received the bulk of the focus at June's Freescale Tech Forum (FTF), i.MX 6 wasn't completely slighted. The company also unveiled the first in a planned series of single-chip system modules (SCMs), based on the i.MX 6Dual application processor and also containing the PF0100 PMIC, 16 MBytes of SPI NOR flash memory, and more than 100 discrete resistors and capacitors (Figure 3). DRAM is missing from the 17x14x1.7 mm package, but a LPDDR2 memory controller and interface are ready for it. And according to System Design and Business Development Manager Navjot Chhabra, 1 and 2 GByte PoP (package on package) assembly support is available for key customer opportunities.

Figure 3. The first in a series of planned single-chip system modules (SCMs) from Freescale integrates pretty much everything you'll need, save for wireless connectivity and DRAM, in a package about the size of a U.S. dime.

This initial SCM and companion development board are in the beta sampling stage, with initial production slated for September; volume pricing has not yet been determined. Chhabra notes that a SCM variant with identical package and pinout and based on the i.MX 6Quad SoC is under development with planned release at year end, and that products enhanced with integrated wireless connectivity are also planned. A SCM based on the i.MX 6SoloX is also under consideration, targeting wearable devices. As for SCMs derived from i.MX 7 application processors, Chhabra and Jedrzejewski both note that no firm decisions have been reached yet.

Finally, for those of you looking for a successor to i.MX 6 and disappointed that i.MX 7 wasn't it, Freescale's Jedrzejewski urges you not give up hope. The i.MX 8 product line is currently in the planning stage of its development cycle, according to Jedrzejewski, with initial sampling currently forecasted to begin some time in 2017 and production to follow roughly a year later. Stay tuned for product specifics; Freescale's candor at this early stage about its future plans is a refreshing change of pace from the close-to-the-vest industry norm. For now, the company's new product offerings should suffice to both keep customers busy and competitors on their toes.

Add new comment